隨著半導體技術的飛速發展,系統級芯片(SoC)的復雜度呈指數級增長,這給驗證工作帶來了前所未有的挑戰。傳統的純軟件仿真或硬件原型驗證方法已難以滿足現代SoC設計對效率和覆蓋率的雙重需求。在此背景下,軟硬件協同驗證技術應運而生,成為提升SoC驗證效率的重要橋梁。

一、SoC驗證的挑戰與現狀

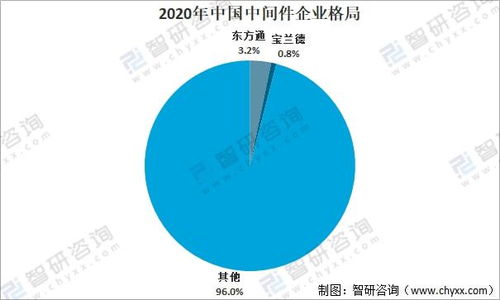

現代SoC集成了處理器核、存儲器、外設接口及專用加速模塊等多種異構組件,其功能交互和時序關系的復雜性使得驗證成為芯片開發中最耗時、最易出錯的環節。據統計,驗證工作占整個芯片開發周期的60%以上,且隨著工藝節點的進步,這一比例仍在持續攀升。

傳統的驗證方法主要依賴軟件仿真和硬件原型驗證兩種路徑。軟件仿真雖具備良好的可控性和可觀測性,但運行速度緩慢,難以應對億門級設計的驗證需求;硬件原型驗證雖運行速度快,但調試困難,且搭建成本高昂。這兩種方法的局限性促使業界尋求更高效的驗證解決方案。

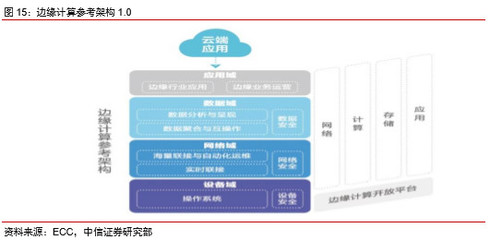

二、軟硬件協同驗證的技術架構

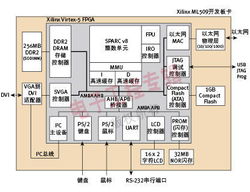

軟硬件協同驗證的核心思想是通過在軟硬件之間建立高效的通信橋梁,實現驗證資源的最優配置。具體而言,該技術架構包含以下關鍵組件:

- 事務級建模(TLM):通過在抽象層次上描述系統行為,實現軟硬件組件的高效互操作。TLM將通信細節與功能實現分離,顯著提升了仿真的運行速度。

- 硬件加速與仿真:采用FPGA或專用硬件加速器運行設計的關鍵部分,同時通過標準化接口與軟件仿真環境保持同步。這種混合驗證模式既保證了運行速度,又維持了調試的便利性。

- 虛擬原型技術:在芯片流片前構建完整的軟件模型,使軟件開發與硬件驗證能夠并行進行。虛擬原型不僅加速了系統集成,還為早期性能分析和架構優化提供了有力支撐。

三、實踐案例與效益分析

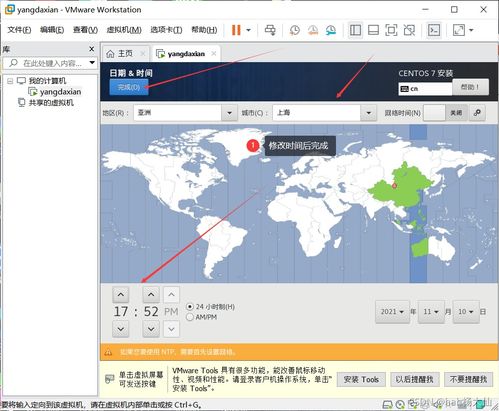

某知名芯片設計公司采用軟硬件協同驗證方法后,驗證周期縮短了40%,缺陷檢出率提升了25%。具體實施策略包括:建立統一的驗證平臺,實現軟硬件驗證環境的無縫對接;采用基于UVM的方法學,提升驗證組件的復用性;引入智能驗證規劃工具,優化驗證資源的分配。

效益分析表明,軟硬件協同驗證不僅直接降低了人力與時間成本,還通過早期錯誤檢測避免了后期修復的高昂代價。更重要的是,該方法為系統級優化提供了數據支撐,有助于提升最終產品的性能與能效。

四、未來發展趨勢

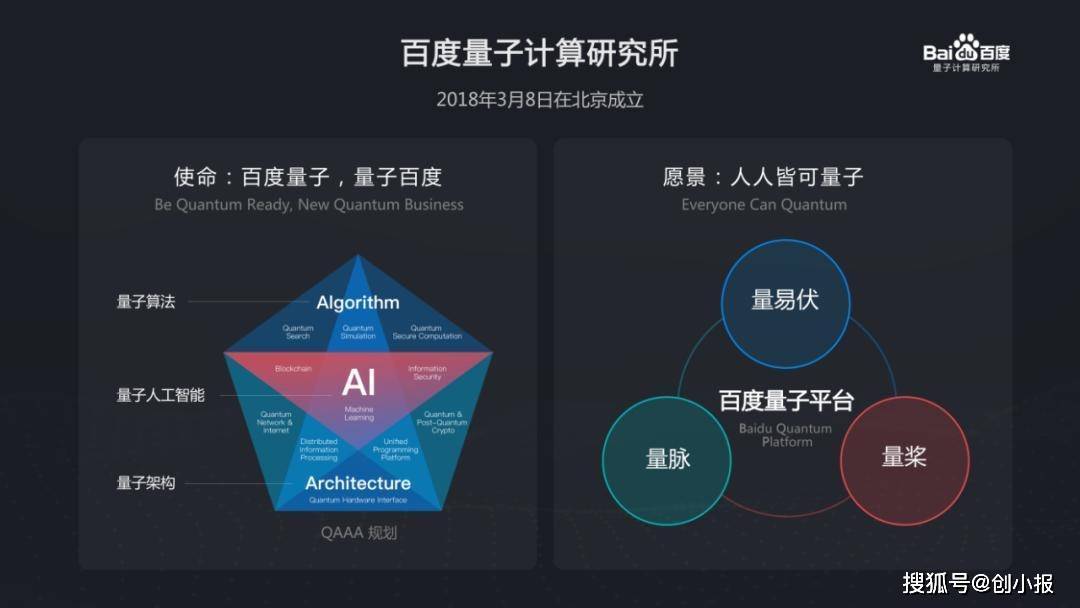

隨著人工智能、5G和物聯網等新興應用的普及,SoC設計將面臨更嚴峻的驗證挑戰。未來軟硬件協同驗證技術將朝著以下方向發展:

- 云原生驗證平臺:利用云計算資源實現驗證任務的彈性伸縮,進一步降低基礎設施成本。

- 智能驗證自動化:結合機器學習技術,實現驗證場景的自動生成與優化,減少人工干預。

- 跨層級協同:打通從算法到硅片的整個設計流程,建立端到端的驗證閉環。

結語

軟硬件協同驗證作為連接計算機軟硬件開發的重要橋梁,已成為提升SoC驗證效率不可或缺的技術手段。通過構建高效的軟硬件交互機制,該技術不僅解決了當前驗證面臨的效率瓶頸,還為應對未來更復雜的設計挑戰奠定了堅實基礎。隨著方法的持續完善與工具的不斷進化,軟硬件協同驗證必將在半導體產業創新中發揮更加關鍵的作用。